前段时间,知名硬件网站Tomshardware援引知情人士的消息称,英伟达为了确保今年的GH200、H200的供应,开出13亿美元的预算,向美光和SK海力士预定了部分HBM3e内存产能。

不过由于这组数据没有合理的计算,13亿的预算的可信度有待确认,但可以肯定的是,这笔预算不可能买空2024年全球HBM的产能。

它的价值在于,可以帮助英伟达抢到2024年上半年“垄断算力”的机会窗口——产品先市场化,就能先抢到市场份额。

2024年,SK海力士、美光和三星三家代工产能总计会扩大到75万片晶圆,按目前业内的数据,HBM3e的良率大概90%左右,每片晶圆约可以切出750颗,全球2024年的HBM总产能大致为5600万颗(12层 + 8层),但是大规模产能集中在下半年开出,上半年比例略小。

倘若基于2024年CoWoS封装产能推算:

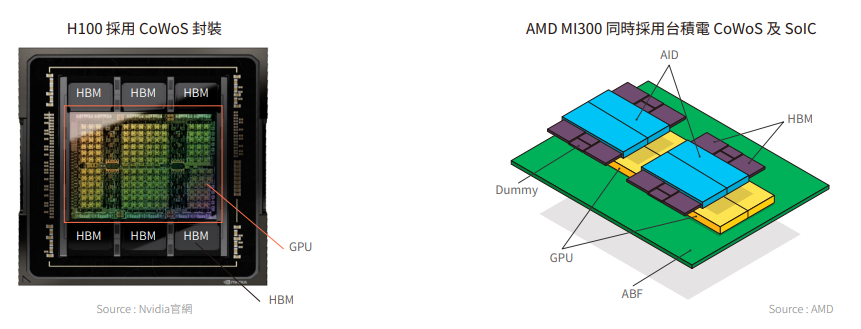

而在GPU-HBM垂直封装的产能方面,截至2024年第4季度,全球CoWoS的封装总产能推算大约30万片晶圆,其中包括台积电约27万片,Amkor约4万片,而由于这些晶圆流片的工艺节点集中在5nm和3nm,当期良率约为38%,保守设定单片晶圆可以切30颗GPU芯片,即2024年全年,全球经由CoWoS封装的GPU产品,产能约为900万颗。按照单颗GPU逻辑芯片搭配6颗HBM内存颗粒的标准计算(AMD MI300搭配8颗HBM),全球2024年的GPU,对HBM内存的需求就在5400万颗以上(12层为主)。

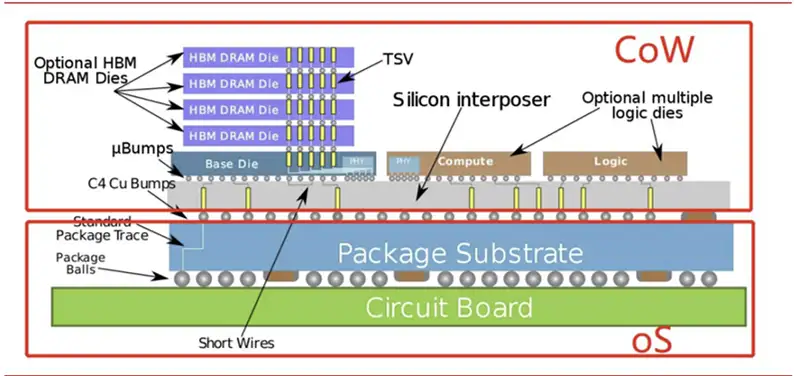

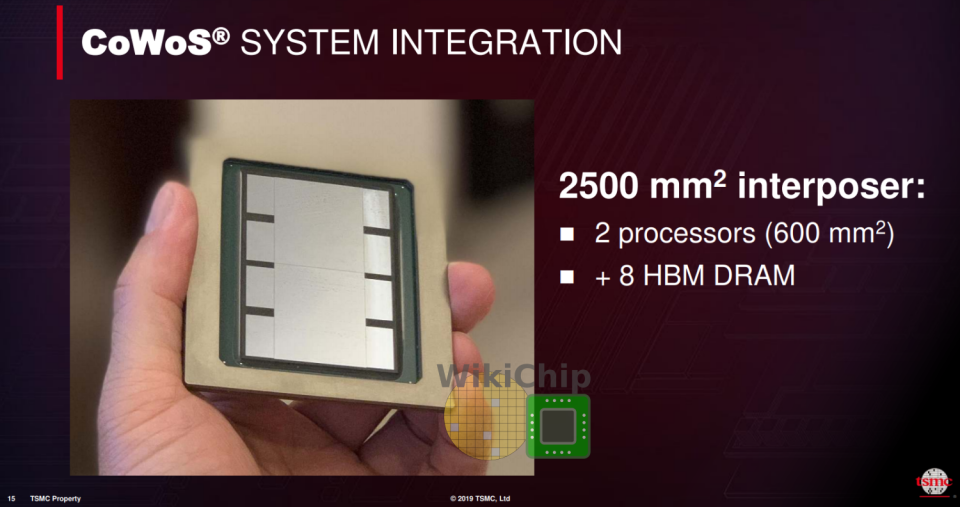

小注释:CoWoS俗称2.5D封装,全称是Chip on Wafer on Substrate,用于在相对理想的电气规则下满足多颗计算芯片的互连以及存储芯片的堆叠实现。

目前,12层HBM颗粒的渠道单价约为每颗250美元+,倘若13亿预算的说法属实,英伟达仅能预订520万颗,仅占HBM全年总产能的1/10。

实际上,根据封装数据的推算,英伟达2024年预定了超过14万片晶圆的CoWoS产能,其中台积电作为“主要供应商”分到12万片,Amkor作为“次级供应商”分到2-3万片,对应GPU总体的产能接近450万颗。

按照每颗GPU逻辑芯片和存储颗粒1:6的比例测算,即英伟达全年需要约2700万颗HBM,基于单颗250美元的成本测算,意味着英伟达全年采购HBM芯片的费用可以预测到68亿美元,远超此前媒体披露的13亿美元预算。

注意:诸如英伟达RTX系列使用GDDR6颗粒的消费级显卡,自然不会计入CoWoS产能;上述的英伟达产能是特指Hopper系列和Blackwell架构的B200,由此估算2024年英伟达的HBM颗粒订单需求是2700万颗。

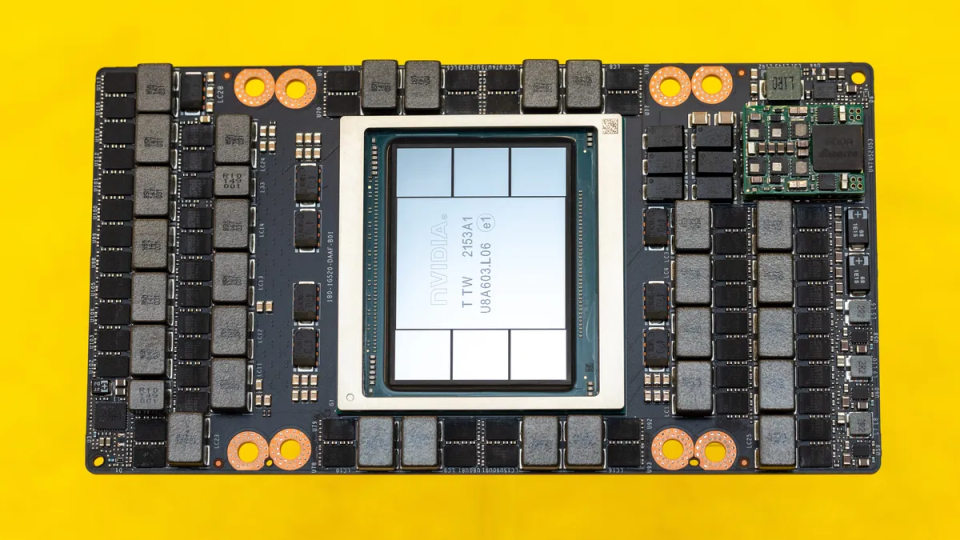

英伟达H100实物图,中间为逻辑芯片,旁边为6颗HBM芯片 来源:网络

HBM产能吃紧的背后

截至2024年第4季度,各家GPU超算产品对应HBM颗粒封装的预定产能大约900万颗,结合2025年海力士/三星/镁光三家内存厂的扩产计划总计近6000万颗HBM(12层为主,8层略少),这两份供应数据就是吻合的,同时也说明2024-2025年的CoWoS和HBM产能是充足的。

不过虽然产能不缺,但是上述数据毕竟是“年度计”,事实上很多产能直到第4季度才会开出,而各家预定的产能当然是越早越好,时效性是关键条件,上半年初的机会窗口更重要,倘若下半年才开始投产,那么产品进入渠道就要等到次年。

另外关于CoWoS产能的扩充,目前主要依赖台积电和Amkor的产能,诸如台联电、格芯等产线,虽然也能做前道65nm的中介层,但由于缺乏先进制程覆盖的能力,即无法代工前道的先进工艺逻辑芯片和中介层,也无法实现一条龙的CoWoS全栈,目前看最有机会的追赶者是三星

三星计划导入全栈CoWoS封装,产品化命名为I-CUBE/H-CUBE,与台积电争夺订单;但是三星在2024年尚且不能开出产能,2025年可能对三星更有利,作为同时供应HBM和CoWoS的IDM厂商,其工艺特点和价格优势是显见的。(未来,三星还会推出X-CUBE 3D封装,统称为SAINT,即三星先进封装技术。)

另外,倘若2025年英特尔的晶圆代工业务顺利实现独立运营,其Intel Foveros封装方案也值得观望。

当前我们看到HBM全球库存和渠道周转十分紧张,实际原因是当期HBM3e供应商仅有SK海力士一家,恰逢大模型高速发展的趋势带来的HBM需求高峰,进而出现供需失衡,但这种失衡会随着产能扩大而减缓。

不过,有一点需要关注,存储颗粒是一种标准品SKU,无需针对颗粒本身做客户化定制,于是这个品类就产生了所谓现货市场。标准现货是可以通过渠道或分销平台正常流通的,即倘若2024年SK海力士、美光和三星三家内存厂规划的产能全部顺利开出,则全球各区域的代理商库存都会充足,无数的次级渠道/次级代理商都可以无限转售。

因此,只要现货库存充足、价格趋势向好,现货市场便永远可以拿货,演变成DRAM现货渠道的业态,这是内存颗粒的产业特性。

这就引发了一个很有意思的话题,倘若出于特殊原因,某个企业无法通过向上述三家订货怎么办?

现货市场就是一个通路——特定企业可以从现货市场采购HBM颗粒,进而再适配控制器、适配I/O和逻辑封装。

倘若现货市场仍然买不到HBM内存,也可以从现货市场采购2D-DRAM颗粒,再通过TSV垂直方向通孔、TCB热压键合(未来更多层堆叠则需要Hybrid Bonding键合)的封装工艺可以堆叠出一个规格不算高的HBM器件。

当然,终极目标就是自研内存颗粒,实现HBM自主产业化。

H100和MI300封装方案图解 来源:网络

参考当下的GPU芯片构型,倘若缺少CoWoS封装结构,HBM甚至无处摆放。

目前全球可选的CoWoS产能供应商有几个类别:

其一是台积电 CoWoS;

其二是由台积电完成晶圆和前道中介层的制造(即CoWoS的“CoW”部分,堆叠+互连),随后交由自家封装厂(例如空闲的InFO产能)或是合作第三方OSAT封装厂,俗称外包封装厂,完成“on Substrate”部分,即封装在基板上;

其三是,可委托由联电、格芯生产中介层,随后再送交Amkor或日月光等OSAT产线,委托完成“WoS”部分。但如前文提到,这两家工艺节点基本在65nm左右,不能代工先进前道的先进工艺逻辑芯片和中介层,也不能完成一条龙的CoWoS全栈;

其四是Samsung I-Cube/H-Cube和Intel Foveros,两家都可以完成全栈CoWoS交付,但目前都还没有开出产能;

其五是国内也有一部分CoWoS的能力,但几乎全部是CoW+WoS的工艺对接,也就是联电、格芯+Amkor、日月光的模式。

相比其它制造工序而言,CoWoS并没有极度前沿的技术门槛,唯一的关键是它要保证在高微缩制程下的高良率。

因为在封装层面,倘若出品有较高的不良/失效,那么上面堆叠连接的HBM等器件就变成无可挽回的损耗了,能够兼顾较高工艺节点和良率的厂商,目前唯有台积电可以满足。

单就CoW+WoS产能而言,全球可以开出很多产能(尤其WoS厂商),但是能够适用于先进计算芯片的工艺/良率的产能则并不多。

导致上述良率门槛的原因是工艺:

以WoS良率为例,难点主要在于其封装的中介层尺寸应当有严格限制,即硅中介层面积需要大于其上面2个甚至多个裸晶的尺寸之和。然而,随着这个尺寸越来越大,第五代CoWoS甚至支持通过一种"2-way lithography stitching approach技术"使得中介层尺寸可以扩到2500mm²,随之带来的工艺风险就是——on wafer,也就是硅晶圆上堆叠时出现边缘扭曲、接角垂直凸等变问题,导致封测后不良,而台积电 CoWoS工艺磨合了10几年,积累大量knowhow,才获得如今可靠的高良率。

台积电对外的技术ppt,硅中介层可达到2500mm² 来源:网络

对于OSAT专业封装厂(包括Amkor/日月光等),工艺良率拉升缓慢也与前段中介层的分开制造有关,虽然CoW+WoS是合理的产业链分工,但是拉升两者共同出品的良率需要两家工艺同步发展。

目前,大陆的先进逻辑芯片和中介层基本是由SMIC制造,再将其委托给OSAT专业封装厂完成WoS封测;而倘若拿不到SMIC的产能,也可以委托联电和格芯代工。

未来可能全球大部分2.5D封装都会是前道+后道合作的模式;前道晶圆厂提供中介层做CoW,后道有载板的做WoS。另外,CoWoS也会更多下沉适用到其它场景,涉及AI-HPC的未来大部分产品都会依赖CoWoS封装,2.5D/3D封装目前来看,晶圆厂还是相比OSAT更具优势。

结 语

随着AI-HPC产业对于HBM内存的高度需求,该器件的产品受众、货值和市场空间都是水涨船高,如今HBM单位售价是传统DRAM的数倍,是DDR5的约5倍。

如前文所述,当期12层HBM颗粒的渠道单价已然250美元/颗,价格相比2023年略有上浮。

换一个测算角度:目前在AI-HPC计算芯片上,通常6颗容量16GB的HBM3颗粒的合计成本约1500美元,相当于15.6美元/GB;换算到H100 SXM5板卡,6颗HBM3 80GB,相当于18.75美元/GB,约占整颗芯片物料成本的50%+。

有一组数据是来自Yole:未来5年先进封装整体复合增速是40%,其中3D封装是超过100%的增速;以及五年后接近40%的HBM都要基于混合键合封装了。

因此,无论海外或是大陆厂商,上述谈到的几个产业方向“HBM、CoW、TSV/Hybrid Bonding”的潜在市场空间是广阔的,期待国产厂商有成熟的良率和进军海外市场的可能。同时随着AI-HPC市场的繁荣,受此驱动,预计将大幅提高HBM在泛DRAM市场的份额,HBM在DRAM市场总容量中的份额预计将从2023年的2%上升到2024年的5%,到2025年将超过10%。

原文始发于微信公众号(腾讯科技):2024,英伟达要花450亿买芯片